Multi-Rate Serdes IP Solution

Multi-Rate Serdes IP Solution

YouPHY-Serdes provides 2.5-32Gbps multi-rate SERDES IP which is designed for smooth integration of Multiple SERDES lanes demonstrate good performance class performance, area and power. The programmable PHY supports major standards such as PCIe Gen 4.0/3.0/2.0/1.0, USB 3.1/3.0, XAUI, SATA Gen 3.0/2.0/1.0, CEI-11G-LR, 10GBase-KX4, JESD204B, SGMII/QSGMII, RAPID I/O, HSSTP (Trace Port), V-By-One, DisplayPort and HMC.

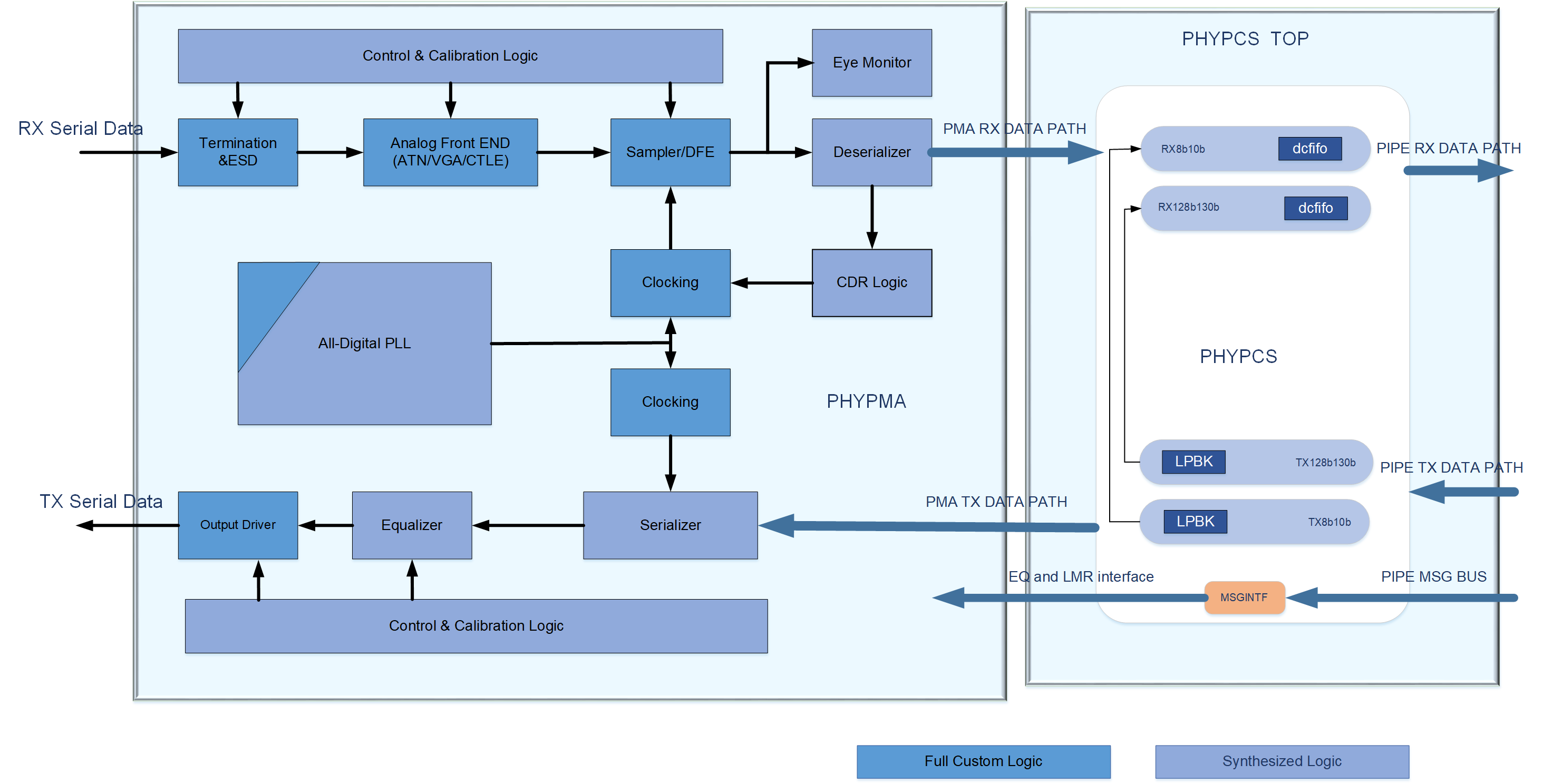

YouSerdes Subsystem

Single SERDES Design that meets wide range of Standards, Protocols and Speeds.

Any combination is possible, e.g. USB3.1, PCIe Gen-4 and SATA Gen3 in a single Combo SERDES.

Internal Low Jitter PLL support the various standards clocking requirements- no need for additional components.

Flexible Design- Tile Based Design that enable customer to select any number of Tx and Rx Lanes.

One Time Effort in design, integration, verification and silicon validation.

Save Chip area as it there is no need to duplicate logic when few standards are required.

Metal stack 1P9M and above

Constant latency of 1.5-word clocks

Maximum 35db Insertion loss support

Flexible macro configurations

Maximum x8 support with a single CMU

Self-adaption of all major calibration and adaptive processes supported for robust performance

Software control and override of all auto-adaption processes supported

Support for both common reference clock and Separate Reference Clock without SSC (SRNS)

SSC supported

Max. of +/-300ppm frequency offset for separate reference clock mode

On-die Eye Monitor for RX performance and TX-to-RX loopback performance

DIR mode for link EQ training supported (PIPE)

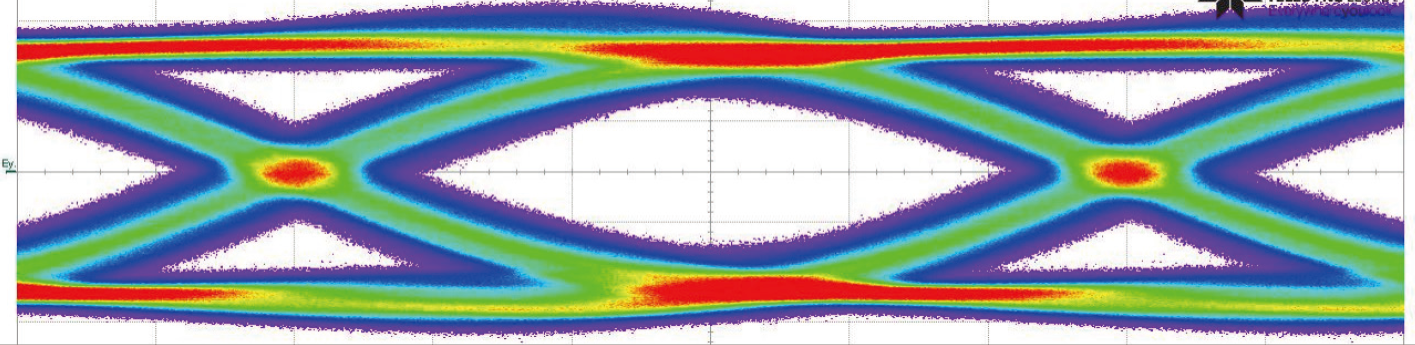

32Gbps Eye Diagram

Datasheet

User's Manual

Package/PCB guideline

SDK (standard design kit) including verilog model, .lib/.db file, .lef file