系统解决方案

系统解决方案

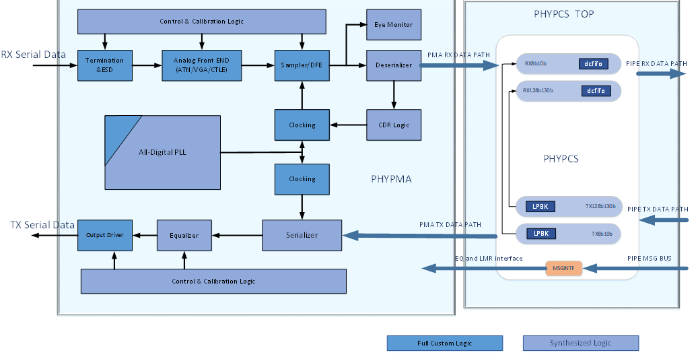

Brite 32Gbps PCIe PHY和控制器解决方案提供了高效的互连,在PPA方面具有明显的优势。该系统可以支持短距离或长距离通道,以满足大量的应用场景。除了具有高线速的PHY的高性能外,低延迟也是Brite 32Gbps PCIe PHY的一个关键特征。该PHY支持2.5Gbps至32Gbps的数据速率,可以覆盖PCIe Gen5.0/4.0/3.0/2.0/1.0。 共用的LC-PLL时钟生成器可以为多达8个数据通道提供高速时钟,数据通道的数量可以进行灵活的宏观配置,例如1x、2x、4x、8x。PCIe PHY的顶层框图见图1。

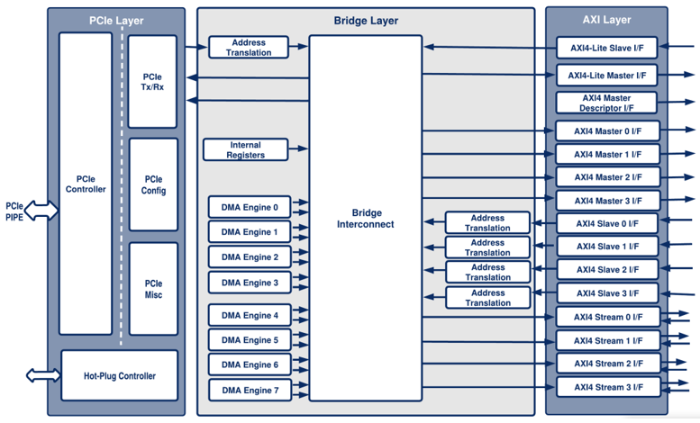

Brite PCIe控制器到AXI架构如图2所示。它在PCI Express和最新版本的AXI协议之间提供了一个高性能、易于使用的互连解决方案。它继承了领先的架构,具有内置DMA的AXI用户界面,符合AMBA® AXI3和AXI4规范。

图1 Brite PCIE PHY框图

图2 : PCIE 控制器 到 AXI 架构

控制器特性:

x1, x2, x4, x8, x16 PCI Express核心

支持每通道2.5、5.0、8.0、16.0和32.0 GT/s的链接速率

8位、16位、32位、64位和128位PIPE接口

符合PCI Express的PHY接口(PIPE),符合修订版4.4.1/5.2

符合PCI Express®基础规范修订版5.0 v1.0

4 KByte最大有效载荷

1个虚拟通道(VC)

支持通道反转

集成时钟域交叉(CDC),支持用户选择的桥接频率

可选的AXI4-Lite从属接口用于网桥配置

用于外部寄存器配置的可选AXI4-Lite主接口

PHY特性:

金属堆栈1P9M,待定

1.5字时钟的恒定延迟

灵活的宏配置

单个CMU最大支持x8

支持所有主要校准和自适应过程的自适应,以获得稳定的性能

支持对所有自动适应过程的软件控制和重写

支持共用参考时钟和无SSC(SRNS)的独立参考时钟

支持SSC

独立参考时钟模式的最大+/-300ppm频率偏移

用于RX性能和TX-to-RX回路性能的片上眼图监测逻辑

支持链接EQ训练的DIR模式(PIPE)

-实现了RX眼图监控

完全符合PCIE Express Base 5.0和4.0,PCI Express Base 3.1/2.1/1.1电气规范

符合PIPE修订版4.4.1/5.2

不同的回路模式:近端串联,远端并联