可配置SoC平台

可配置SoC平台

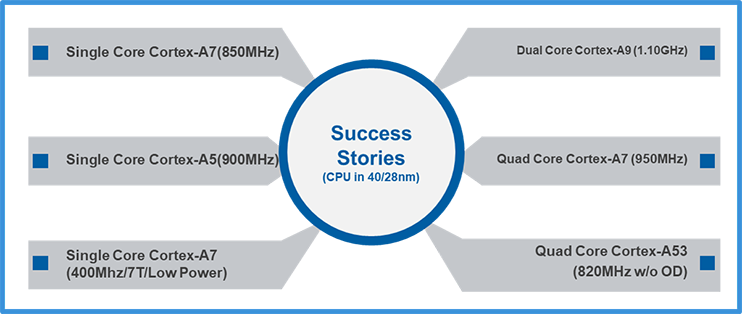

YouSiP-AP是基于ARM Cortex A系列核架构的处理器SoC平台原型,已经在40纳米和28纳米工艺上流片验证成功,拥有众多客户采用该SoC平台成功开发产品的实际案例。该平台原型可以为客户提供完整的开发工具,包括ISP/ICP工具、开发板、参考代码、程序和外围IP,帮助客户缩短SoC产品的上市时间,提高一次流片成功率,赢得在工业控制、家电应用、安防、玩具和移动终端等市场中的新兴机会。

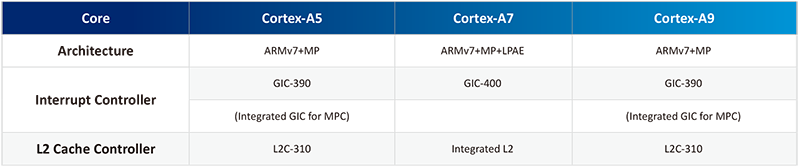

Cortex-A9/A7/A5处理器通过扩展所需的峰值性能点和可伸缩性,提供所需的电力效率和硅成本,同时保持完全的软件兼容性,提供了设计灵活性。

Cortex-A9处理器可作为1-4核多核处理器,具有缓存一致性、集成外围设备和高级总线接口选项的额外优势。灿芯的双核硬宏在40LL工艺下实现,可在25℃,TT下达到1.3GHz。该宏提供了一个低风险、加速的路径,为各种高性能市场提供低功耗解决方案。

Cortex-A7处理器在功耗和面积上与超节能的Cortex-A5处理器相似,但性能比前者高出15~20%。高级特性包括大型物理地址扩展(LPAE)、硬件虚拟化支持和AMBA4 ACE (AMBA Coherency Extension)。对于想要将最新的低成本智能手机和平板电脑应用程序作为独立处理器的客户来说,这款小而高效的CPU是理想的。

Cortex-A5处理器是最小的,最低功率多核处理器能够提供互联网尽可能广泛的设备:超低价手机,功能手机和智能移动设备,普遍的低功耗嵌入式解决方案的性能和丰富的UI需求高,消费者和工业设备。Cortex-A5处理器与Cortex-A9完全兼容,功率和面积仅为Cortex-A9的1/3,使灿芯的客户能够立即访问包括Android、Adobe Flash、Java平台标准版(Java SE)、JavaFX、Linux、Microsoft Windows Embedded、Symbian和Ubuntu在内的成熟的开发人员和软件生态系统。

YouSiP-AP 40纳米高性能 CPU核

● 基于高精度40纳米低功耗模型,流片性能与仿真一致

● 漏电电流小于 40mA@1.2V TT wafer in 25oC

● 已完成多种类型的FPGA系统验证,可供客户参考

● 客户早期软件和功能开发可以在这些FPGA验证系统上实现

灿芯半导体YouSiP-AP的成功案例

● 灿芯半导体已完成超过20个ARM Cortex

● 通过强大的技术能力,可以使SoC项目从应用的视角启动